Yang and Wang

Phase – Locked Loops

A project for ECE 547 “VLSI Design”

Fall Semester 2001 at the

Electrical Engineering Dept.

University of Maine

Designed by

Fan Yang and Dali Wang

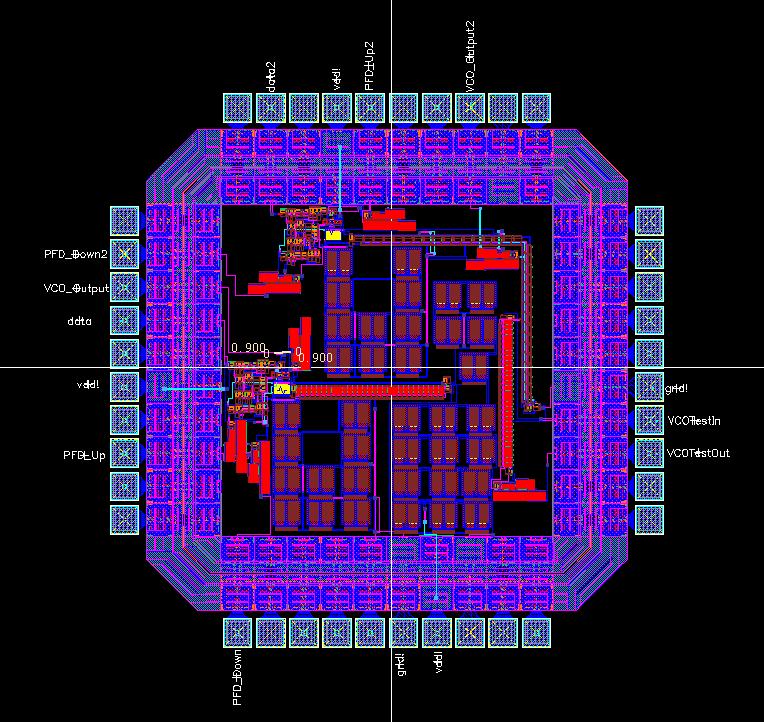

This is our final project for ECE 547 — Digital Phase Locked Loops. The final layout is shown above. It consists of two sets of PLLs. One is designed for the input digital signals whose frequency is around 20MHz, the other is for 25MHz. Each PLL has three major parts — phase & frequency detector, loop filter and voltage controlled oscillator.

Here is our final report (PDF) and its contents (PDF).

Test results (PDF) and a poster (PDF) describing our project are also available.

August 2002