Rahman 2010

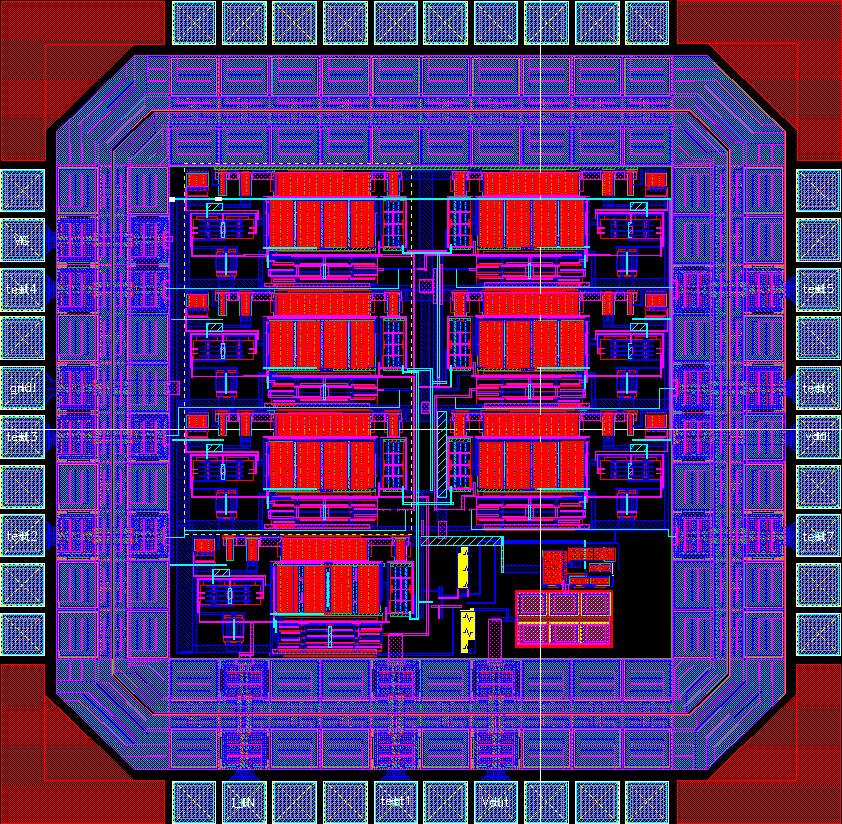

120 dB Pseudo Logarithmic Amplifier

A project for ECE 547 “VLSI Design”

Fall Semester 2010

Electrical Engineering Dept. of the University of Maine

Designed by

Faisel Rahman

The overall design consists of a cascade of current limiting amplifiers followed by a difference amplifier. The pseudo-logarithmic amplifier accepts a single ended current input from 1nA to 1mA and produces a single ended voltage output that is pseudo-logarithmic representation of the input current. The rail to rail voltage of the amplifier is 5V, and the range of the output voltage is from 1V to 4V. A 7 stage configuration is applied to meet the desired dynamic input dynamic range of 120dB. The most important feature of these current amplifiers is that they are limiting. That is, there is a set value of current that cannot be exceeded no matter how great the input current may be. The design is implemented so the 1st amplifier has a gain of 9 and the following 6 amplifiers have a gain of 10. Each amplifier has three outputs, Iout, Isum1 and Isum2. The Iout of the 1st amplifer is the Iin for the 2nd amplifer and so on. All the Isum1 and Isum2 gets added to give to logarithmic current output; Isum1 having a possitive value and Isum2 having a negative value. These two currents are the inputs of the difference amplifier which provides a corresponding linear voltage from 1V to 4V.

The project report (PDF) contains a description of the project and details of the design and layout.

Fall 2010