Tumati

10-bit D/A Converter for a 50MHz Direct Digital Synthesizer

VLSI Analog Design Project

ECE 547 — Spring 2006

Electrical & Computer Engineering Department

University of Maine

Designed by

Raghu Tumati

Other blocks desgined by

Aravind Reghu (12-bit Pipeline Accumulator)

Ogy Nikolic (8-bit ROM Pointer)

Cyrus Miller and Anusha Ramanujam (4×64-bit ROM)

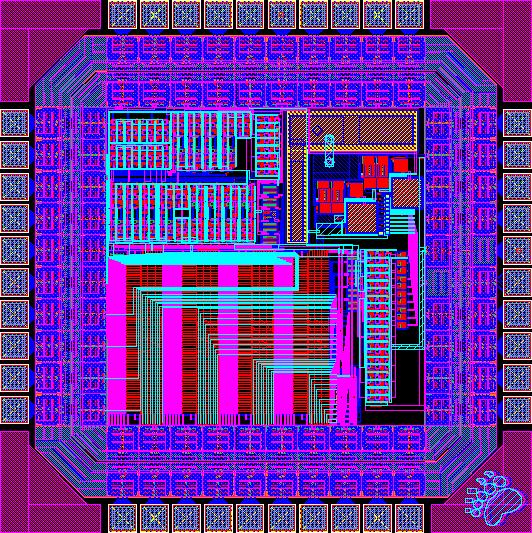

Layout of 50MHz DDSThe IC generates a 25MHz sinusoidal waveform centered at 3.5V with an amplitude of 0.5V (Vpp = 1V) when given a 12-bit binary input that count from 000h through FFFh with transitions occuring at 50MHz. The major design blocks include a 12-bit Accumulator, 8-bit ROM Pointer, 4×64-bit ROM and a 10-bit DAC. See schematic in Figure 2 below. My part consists of the Digital to Analog converter built by a R-2R ladder configuration.The Op-Amp for the DAC is a two stage amplifier in a unity gain feedback configuration with an open loop gain of 2500 to aquire 10 bit precision. Its gain Bandwidth is 50Mhz

Complete project details are available in the project report (PDF).