Reghu

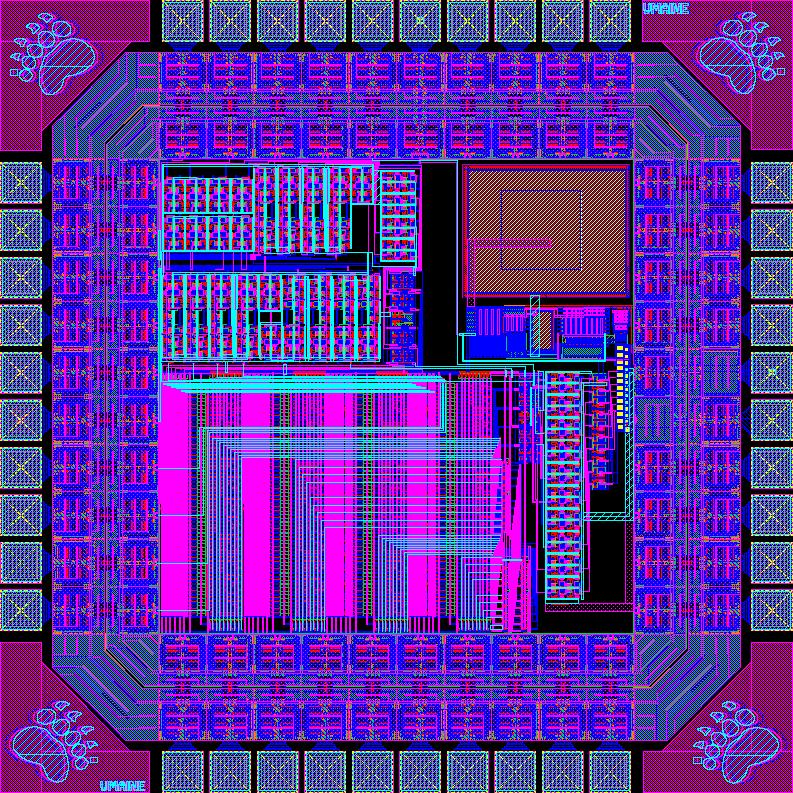

12 Bit Accumulator for Direct Digital Synthesizer

A project for ECE 547 “VLSI Design/Layout”

Spring Semester 2006

Electrical Engineering Dept.

University of Maine

Designed By

Aravind Reghu

Other Parts Designed By

Anusha Ramanujam and Cyrus Miller (4×64-bit ROM)

Stephen Fortune (10-bit DAC)

Ogy Nikolic (8-bit ROM Pointer)

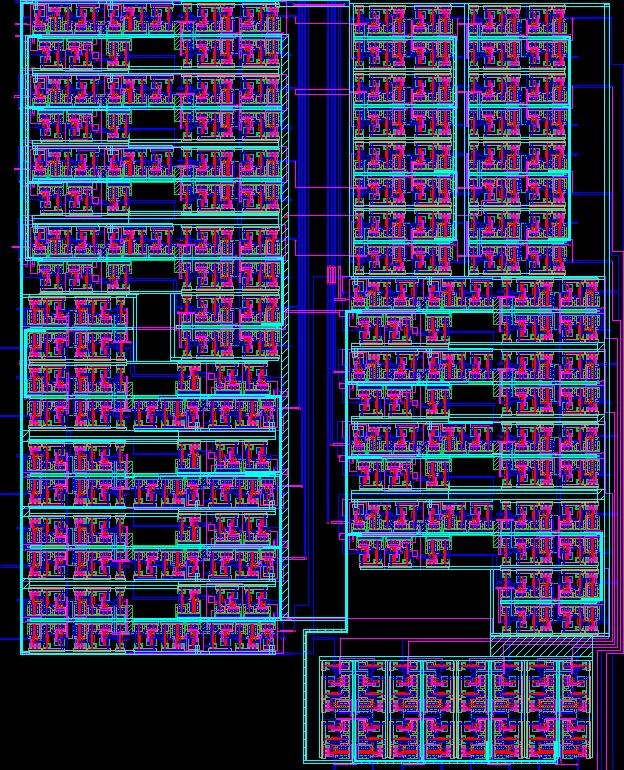

Direct Digital Synthesizers(DDSs) are widely used in applications such as radios, instrumentation and radar systems.They are known for their highly accurate digital tuning,low noise figure, and phase-continuous frequency-hopping capabilities. The basic components in the layout consists of a 12 Bit Pipelined Accumulator,a ROM Pointer , a 256 Bit ROM and a 10 Bit DAC.The 12 Bit Accumulator which I have designed is made up of three pipelined 4 bit Accumulators.The accumulator is designed to operate at a clock frequency of 50 Mz with inputs varying from 000h to FFFh.The output of the DDS chip is a sinusoidal wave having a frequency of 25Mz and a peak to peak voltage of 1.7V.

The Layout of 12 Bit Pipelined Accumulator

The project report (PDF) contains a description of the project, details of the design, simulation results, and layout.

May, 2006