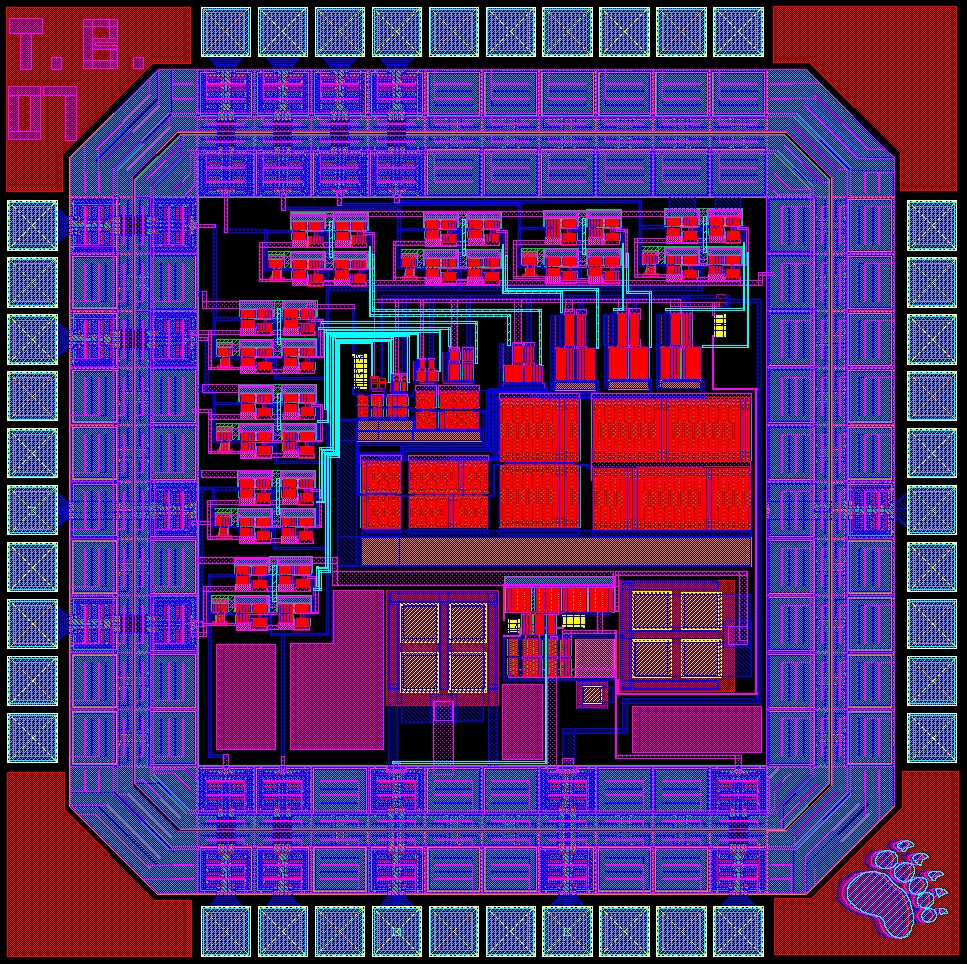

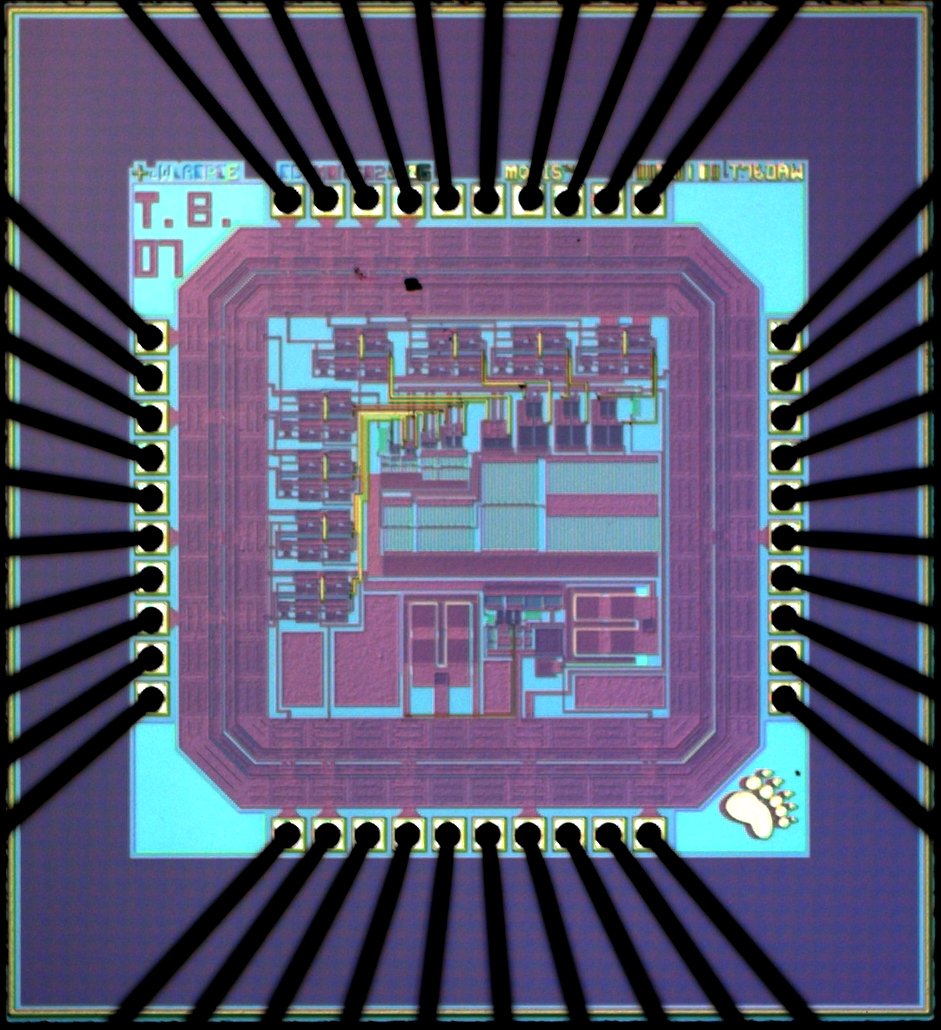

Bellamine

8 Bit Current Steering DAC

A project for ECE 547 “VLSI Design”

Spring Semester 2007

Dept. of Electrical and Computer Engineering

University of Maine

Designed by

Taoufiq Bellamine

This chip

Consists of an 8 Bit Current Steering DAC operating from three supplies of 5v, 2.5v and 3.5v. The process used for this purpose is a 0.5 um CMOS process. The fact that the current steering topology is used instead of the R2R topology made it more challenging to achieve a good INL as well as DNL results. Glitching power from clock feed through and signal coupling was minimized through the use of special latches and charge injection switches. The Op Amp used in this project was designed to have a 90 dB open loop gain and a 20 MHz unity bandwidth. The output range of the DAC was in the order of 1.96 v with an LSB of 8.2 mv.

The Design Project Report (PDF) contains a description of the project and details of the design and layout.

The Test Results Report (PDF) contains the test results of the manufactured design.

Last Updated Dec 2007